Gut, mit der Bezeichnung wage ich an dieser Stelle natürlich den tiefen Griff in die Spekulatius-Kiste, aber sehen wir das Ganze doch einfach mal sportlich und exemplarisch, denn irgendwie muss man das Teil ja (vorerst) mal nennen. Die Rede ist hier von AMDs neuem 16-Kerner (32 Threads), der sich immer mehr materialisiert und damit natürlich auch auffindbare Spuren hinterlässt.

Ich hatte ja bereits exklusiv über das B0-Stepping berichtet, aber die aktuellen OPN, also quasi die Bestellnummern der CPU, geben da schon mehr Anlass zur Freude und natürlich auch für eine neue News. Also mache ich (mal wieder) den i-machi und teile die neuesten Erkenntnisse mit Euch. Ein klein wenig Click-Bait im Titel sei mir also gestattet, denn es ist exklusiver Inhalt und die Quellen sind, wie so oft, meine eigenen.

Mehr Boost-Takt und ein solider Basistakt

Kommen wir zunächst zum Takt, also dem, was die meisten an erster Stelle interessiert. Das, was gerade von den einschlägigen Unternehmen zum Testen geordert werden kann, hört auf den Namen 100-000000059-52_48/35_Y. Gut, der erste Teil der OPN ist nicht neu, die hatte ich ja bereits schon veröffentlicht, aber am Schluss steht ja auch noch die Klassifizierung für den Takt. Und genau das sehen bis zu 4.8 GHz Boost-Takt für einzelne und 3.5 GHz Basis-Takt für alle 16 Kerne schon mal recht gut aus.

100-000000059-52_48/35_Y

Damit sollten sich die Taktraten dann wohl auch dem finalen Maximum angenähert haben, denn bis zum kolportierten Launch ist es nicht mehr allzu lange hin und irgendwann müssen ja auch die fertigen Samples noch auf Herz und Nieren getestet werden. Wie man die 4.8 GHz aber nunmehr erreicht, hat sicher mehrere Gründe, aber einen davon habe ich auch noch exklusiv für Euch, denn es wird auch eine neue Spielwiese für Übertakter geben. Doch dazu gleich mehr.

Neue Features und ein interessantes Changelog

Als Intel die CPUs der 10. Generation vorgestellt hat, war eine der begleitenden Neuerungen die separierte Vcore-Optimierung für jeden einzelnen Kern, also das, was man per core voltage adjustments nennt. Genau damit schaffte es Intel ja auch, aus einer eigentlich alten und unterlegenen Strukturbreite noch eine wirklich akzeptable Performance herauszupressen. Interessant wird dieses Feature auch für Übertakter und es wird interessant sein zu sehen, wie man das Feature in das Ryzen Master Tool integrieren wird.

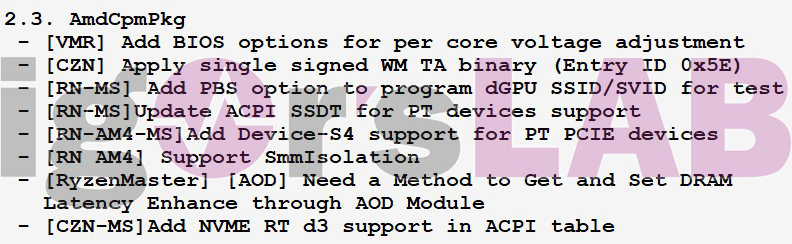

Genau da wird AMD nun analog zu Intel ebenfalls ansetzen, wie uns das Changelog ComboAM4v2PI 1.0.6.0 mitteilt, auch wenn man intern bereits bei Revision 8 angekommen ist. Die Bedeutung der Zahlen der jeweiligen Minors hatte ich Euch ja schon einmal im Artikel „AMD UEFI Inside: Was verbirgt sich wirklich hinter AGESA, dem PSP (Platform Security Processor) und vor allem auch ComboPI?“ erklärt.

Interessant ist hier der der erste Eintrag, der genau diese Funktion beschreibt. Die in eckige Klammern gesetzten Kürzel stehen dabei übrigens für die jeweiligen Chips, also VMR für Vermeer, RN für Renoir usw. Der Eintrag für Cezanne (CZN) offenbart letztendlich, dass es auch für diese APU bereits lauffähige Exemplare zu geben scheint.

Darüber hinaus lässt sich in der Firmware auch per port TXCLK gating finden, was auf eine Effizienzsteigerung hindeutet. Intelligente Taktsteuerungstechniken werden nämlich gern verwendet, um die Aktivität in genau den Teilen einer Schaltung zu minimieren, die nichts zum Gesamtergebnis für diesen bestimmten Taktzyklus beitragen. Diese Taktsteuerung reduziert die dynamische Leistung, indem sie verhindert, dass die Schaltungs-Logik, die in einem bestimmten Taktzyklus nicht verwendet wird, überhaupt erst in diesen Taktzyklus umschaltet.

Zusätzlich verhindert sie die Taktung in den Fällen, in denen keine neuen Daten erzeugt oder diese in einem bestimmten Taktzyklus nicht von der nachfolgenden Logik verwendet werden müssen. Diese Gating-Techniken führen so zu einer deutlich geringeren Dynamik und Gesamtleistungsaufnahme einer Schaltung bei Teil-Lasten.

Dazu passt auch der neue BIOS-Eintrag Enable VCN/FCLK deep sleep, also eine weitere Energiesparoption, die im Übrigen keinem speziellen Modell zugewiesen wurde und damit in Zukunft vielleicht sogar allen CPUs und APUs zugute kommen könnte. Wenn VCN dabei für Video Core Next steht, dann betrifft dies dann als zusätzliches Feature auch die APUs mit integrierter Grafikeinheit.

Der Eintrag Add NVME RT d3 support ist ebenfalls hochinteressant, denn im Zustand Runtime D3 (RTD3) wird der Controller des NVMe-Laufwerks von der eigentlichen Betriebsspannung getrennt. Weitere Versorgungsspannungen können weiterhin bereitgestellt werden oder auch nicht („aux power“). Für PCI Express ist RTD3 nämlich der sogenannte D3cold-Stromzustand. Gut für mobile Endgeräte ist dies allemal. Der Rest der Einträge ist ebenfalls nicht langweilig, betrifft aber überwiegend Renoir und diverse Verbesserungen (Fine Tuning).

Source: eigene

Kommentieren